## CHAPTER

# 12

## LARGE COMPUTER SYSTEMS

## **CHAPTER OBJECTIVES**

In this chapter you will learn about:

- Large computer systems that consist of multiple processors, or multiple computers

- Different structures for implementing multiprocessors

- Interconnection networks and LANs

- Memory organization in multiprocessors

- Cache coherence for shared data

- Shared-memory and message-passing paradigms

- Performance issues in multiprocessor systems

When a computer application requires a very large amount of computation to be completed in a reasonable amount of time, we must use machines with correspondingly large computing capacity. Such machines are often called *supercomputers*. Typical applications that require supercomputers include weather forecasting, finite element analysis in structural design, fluid flow analysis, simulation of large complex physical systems, and computer-aided design (CAD). None of the machines discussed in previous chapters are in the supercomputer class.

A high-performance processor can be designed using fast circuit technology and architectural features such as multiple functional units, pipelining, large caches, interleaved main memory, and separate buses for instructions and data. All these possibilities are exploited in ongoing research and development efforts by many manufacturers to produce processors intended primarily for use in workstations. Their quest is to increase performance without substantially increasing cost, and the results have been spectacular — we now have workstations that outperform machines that were considered to be in the supercomputer class only a decade ago.

However, many applications still demand computing power that greatly exceeds the capability of workstations. Thus, the need for supercomputing power remains strong. One approach is to build a supercomputer that has only a few very powerful processing units. This is typically done by using the fastest possible circuits, wide paths for accessing a large main memory, and extensive I/O capability. Such computers dissipate considerable power and require expensive cooling arrangements. In computationally demanding applications, supercomputers are needed to handle vectors of data, where a vector is a linear array of numbers (elements), as efficiently as possible. Single operations are often performed on entire vectors. For example, an add operation may generate a vector that is the element-by-element sum of two 64-element vectors. Also, a single memory access operation can cause an entire vector to be transferred between the main memory and processor registers. If an application is conducive to vector processing, then computers that feature a vector architecture provide excellent performance. Supercomputers of this class have been marketed by companies such as Cray (Cray-1, Y-MP, and SV1), Fujitsu (VP5000), Hitachi (SR8000), and NEC (SX-5). The main drawback of such machines has been their high cost — both the purchase price and the operating and maintenance cost.

An attractive alternative for providing supercomputing power is to use a large number of processors designed for the workstation market. This can be done in two basic ways. The first possibility is to build a machine that includes an efficient high-bandwidth medium for communication among the multiple processors, memory modules, and I/O devices. Such machines are usually referred to as *multiprocessors*. The second possibility is to implement a system using many workstations connected by a local area communication network. Systems of this type are often called *distributed computer systems*. Multiprocessors and distributed computer systems have many similarities. The former offer superior performance but at a higher price. The latter are naturally available in a modern computing environment at low cost. In the remainder of this chapter, we discuss the salient characteristics of each of these types. They provide large computing capabilities at a reasonable cost.

A system that uses many processors derives its high performance from the fact that many computations can proceed in parallel. The difficulty in using such a system efficiently is that it may not be easy to break an application down into small tasks that can be assigned to individual processors for simultaneous execution. Determining these tasks and then scheduling and coordinating their execution in multiple processors requires sophisticated software and hardware techniques. We consider these issues later in the chapter.

#### 12.1 FORMS OF PARALLEL PROCESSING

Many opportunities are available for parts of a given computational task to be executed in parallel. We have already seen several of them in earlier chapters. For example, in handling I/O operations, most computer systems have hardware that performs direct memory access (DMA) between an I/O device and main memory. The transfer of data in either direction between the main memory and a magnetic disk can be accomplished under the direction of a DMA controller that operates in parallel with the processor.

When a block of data is to be transferred from disk to main memory, the processor initiates the transfer by sending instructions to the DMA controller. While the controller transfers the required data using cycle stealing, the processor continues to perform some computation that is unrelated to the data transfer. When the controller completes the transfer, it sends an interrupt request to the processor to signal that the requested data are available in the main memory. In response, the processor switches to a computation that uses the data.

This simple example illustrates two fundamental aspects of parallel processing. First, the overall task has the property that some of its subtasks can be done in parallel by different hardware components. In this example, a processor computation and an I/O transfer are performed in parallel by the processor and the DMA controller. Second, some means must exist for initiating and coordinating the parallel activity. Initiation occurs when the processor sets up the DMA transfer and then continues with another computation. When the transfer is completed, the coordination is achieved by the interrupt signal sent from the DMA controller to the processor. This allows the processor to begin the computation that operates on the transferred data.

The preceding example illustrates a simple case of parallelism involving only two tasks. In general, large computations can be divided into many parts that can be performed in parallel. Several hardware structures can be used to support such parallel computations.

## 12.1.1 CLASSIFICATION OF PARALLEL STRUCTURES

A general classification of parallel processing has been proposed by Flynn [1]. In this classification, a single-processor computer system is called a *Single Instruction stream*, *Single Data stream* (SISD) system. A program executed by the processor constitutes the single instruction stream, and the sequence of data items that it operates on constitutes the single data stream. In the second scheme, a single stream of instructions is broadcast to a number of processors. Each processor operates on its own data. This scheme.

in which all processors execute the same program but operate on different data, is called a *Single Instruction stream*, *Multiple Data stream* (SIMD) system. The multiple data streams are the sequences of data items accessed by the individual processors in their own memories. The third scheme involves a number of independent processors, each executing a different program and accessing its own sequence of data items. Such machines are called *Multiple Instruction stream*, *Multiple Data stream* (MIMD) systems. The fourth possibility is a *Multiple Instruction stream*, *Single Data stream* (MISD) system. In such a system, a common data structure is manipulated by separate processors, each executing a different program. This form of computation does not occur often in practice, so it is not pursued here.

This chapter concentrates on MIMD structures because they are most useful for general purposes. However, we first briefly consider the SIMD structure to illustrate the kind of applications for which it is well-suited.

#### **12.2** ARRAY PROCESSORS

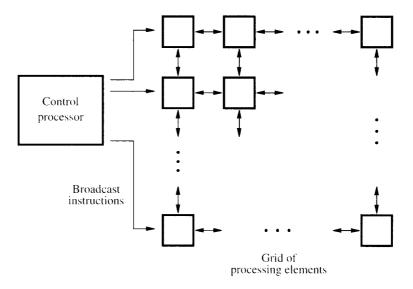

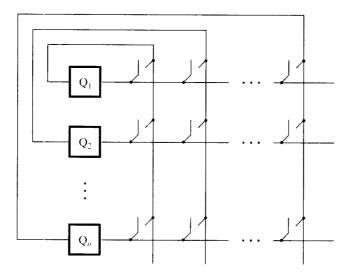

The SIMD form of parallel processing, also called *array processing*, was the first form of parallel processing to be studied and implemented. In the early 1970s, a system named ILLIAC-IV [2] was designed at the University of Illinois using this approach and was later built by Burroughs Corporation. Figure 12.1 illustrates the structure of an array processor. A two-dimensional grid of processing elements executes an instruction stream that is *broadcast* from a central control processor. As each instruction is broadcast, all elements execute it simultaneously. Each processing element is connected to

Figure 12.1 An array processor.

its four nearest neighbors for purposes of exchanging data. End-around connections may be provided in both rows and columns, but they are not shown in the figure.

Let us consider a specific computation in order to understand the capabilities of the SIMD architecture. The grid of processing elements can be used to solve two-dimensional problems. For example, if each element of the grid represents a point in space, the array can be used to compute the temperature at points in the interior of a conducting plane. Assume that the edges of the plane are held at some fixed temperatures. An approximate solution at the discrete points represented by the processing elements is derived as follows. The outer edges are initialized to the specified temperatures. All interior points are initialized to arbitrary values, not necessarily the same. Iterations are then executed in parallel at each element. Each iteration consists of calculating an improved estimate of the temperature at a point by averaging the current values of its four nearest neighbors. The process stops when changes in the estimates during successive iterations are less than some predefined small quantity.

The capability needed in the array processor to perform such calculations is quite simple. Each element must be able to exchange values with each of its neighbors over the paths shown in the figure. Each processing element has a few registers and some local memory to store data. It also has a register, which we can call the network register, that facilitates movement of values to and from its neighbors. The central processor can broadcast an instruction to shift the values in the network registers one step up, down, left, or right. Each processing element also contains an ALU to execute arithmetic instructions broadcast by the control processor. Using these basic facilities, a sequence of instructions can be broadcast repeatedly to implement the iterative loop. The control processor must be able to determine when each of the processing elements has developed its component of the temperature to the required accuracy. To do this, each element sets an internal status bit to 1 to indicate this condition. The grid interconnections include a facility that allows the controller to detect when all status bits are set at the end of an iteration.

An interesting question with respect to array processors is whether it is better to use a relatively small number of powerful processors or a large number of very simple processors. ILLIAC-IV is an example of the former choice. Its 64 processors had a 64-bit internal structure. Array processors introduced in the late 1980s are examples of the latter choice. The CM-2 machine produced by the Thinking Machines Corporation could accommodate up to 65,536 processors, but each processor is only one bit wide. Maspar's MP-1216 has a maximum of 16,384 processors that are 4 bits wide. The Cambridge Parallel Processing Gamma II Plus machines can have up to 4096 processors that can operate on either byte-sized or bit-sized operands. These choices reflect the belief that, in the SIMD environment, it is more useful to have a high degree of parallelism rather than to have fewer but more powerful processors.

Array processors are highly specialized machines. They are well-suited to numerical problems that can be expressed in matrix or vector format. Recall that supercomputers with a vector architecture are also suitable for solving such problems. A key difference between vector-based machines and array processors is that the former achieve high performance through heavy use of pipelining, whereas the latter provide extensive parallelism by replication of computing modules. Neither array processors nor vector-based machines are particularly useful in speeding up general computations, and they do not have a large commercial market.

## 12.3 THE STRUCTURE OF GENERAL-PURPOSE MULTIPROCESSORS

The array processor architecture described in the preceding section is a design for a computer system that corresponds directly to a class of computational problems that exhibit an obvious form of data parallelism. In more general cases in which parallelism is not so obvious, it is useful to have an MIMD architecture, which involves a number of processors capable of independently executing different routines in parallel.

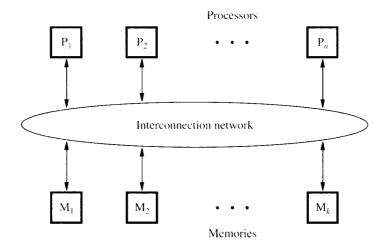

Figures 12.2, 12.3, and 12.4 show three possible ways of implementing a multiprocessor system. The most obvious scheme is given in Figure 12.2. An *interconnection network* permits *n* processors to access *k* memories so that any of the processors can access any of the memories. The interconnection network may introduce considerable delay between a processor and a memory. If this delay is the same for all accesses to memory, which is common for this organization, then such a machine is called

Figure 12.2 A UMA multiprocessor.

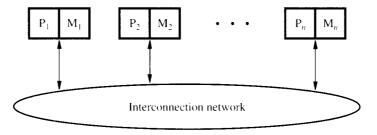

Figure 12.3 A NUMA multiprocessor.

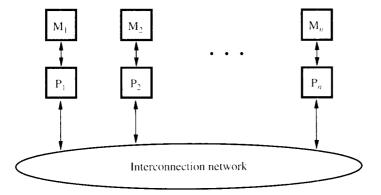

Figure 12.4 A distributed memory system.

a Uniform Memory Access (UMA) multiprocessor. Because of the extremely short instruction execution times achievable by processors, the network delay in fetching instructions and data from the memories is unacceptable if it is too long. Unfortunately, interconnection networks with very short delays are costly and complex to implement.

An attractive alternative, which allows a high computation rate to be sustained in all processors, is to attach the memory modules directly to the processors. This organization is shown in Figure 12.3. In addition to accessing its local memory, each processor can also access other memories over the network. Since the remote accesses pass through the network, these accesses take considerably longer than accesses to the local memory. Because of this difference in access times, such multiprocessors are called Non-Uniform Memory Access (NUMA) multiprocessors.

The organizations of Figures 12.2 and 12.3 provide a *global memory*, where any processor can access any memory module without intervention by another processor. A different way of organizing the system is shown in Figure 12.4. Here, all memory modules serve as private memories for the processors that are directly connected to them. A processor cannot access a remote memory without the cooperation of the remote processor. This cooperation takes place in the form of messages exchanged by the processors. Such systems are often called *distributed-memory* systems with a *message-passing protocol*.

The preceding discussion uses processors and memory modules as the main functional units in a multiprocessor system. Although we have not discussed I/O modules explicitly, any multiprocessor must provide extensive I/O capability. This capability can be provided in different ways. Separate I/O modules can be connected directly to the network, providing standard I/O interfaces, as discussed in Chapter 4. Some I/O functions can also be incorporated into the processor modules.

Figures 12.2, 12.3, and 12.4 depict a high-level view of possible multiprocessor organizations. The performance and cost of these machines depend greatly on implementation details. In the next two sections, we consider the most popular schemes for realizing the communication network and the structure of the memory hierarchy.

## **12.4** Interconnection Networks

In this section, we examine some of the possibilities for implementing the interconnection network in multiprocessor systems. In general, the network must allow information transfer between any pair of modules in the system. The network may also be used to broadcast information from one module to many other modules. The traffic in the network consists of requests (such as read and write), data transfers, and various commands.

The suitability of a particular network is judged in terms of cost, bandwidth, effective throughput, and ease of implementation. The term *bandwidth* refers to the capacity of a transmission link to transfer data and is expressed in bits or bytes per second. The *effective throughput* is the actual rate of data transfer. This rate is less than the available bandwidth because a given link usually does not carry data all of the time.

Information transfer through the network usually takes place in the form of *packets* of fixed length and specified format. For example, a read request is likely to be a single packet that contains the addresses of the source (the processor module) and destination (the memory module) and a command field that indicates what type of read operation is required. A write request that writes one word in a memory module is also likely to be a single packet that includes the data to be written. On the other hand, a read response that involves an entire cache block requires several packets. Longer messages may require many packets.

Ideally, a complete packet would be handled in parallel in one clock cycle at any node or switch in the network. This implies having wide links, comprising many wires. However, to reduce cost and complexity, the links are often considerably narrower. In such cases, a packet must be divided into smaller pieces, each of which can be transmitted in one clock cycle.

#### **12.4.1 SINGLE BUS**

The simplest and most economical means for interconnecting a number of modules is to use a single bus. The detailed aspects of bus design, as discussed in Chapter 4, apply here as well. Since several modules are connected to the bus and any module can request a data transfer at any time, it is essential to have an efficient bus arbitration scheme. Examples of such schemes are given in Chapter 4.

In a simple mode of operation, the bus is dedicated to a particular source-destination pair for the full duration of the requested transfer. For example, when a processor issues a read request on the bus, it holds the bus until it receives the desired data from the memory module. Since the memory module needs a certain amount of time to access the data (as discussed in Chapter 5), the bus will be idle until the memory is ready to respond with the data. Then the data are transferred to the processor. When this transfer is completed, the bus can be assigned to handle another request.

Suppose that a bus transfer takes T time units, and the memory access time is 4T units. It then takes 6T units to complete a read request. Thus, the bus is idle for two-thirds of the time. A scheme known as the *split-transaction protocol* makes it possible to use the bus during the idle period to serve another request. Consider the following

method of handling a series of read requests, possibly from different processors. After transferring the address involved in the first request, the bus may be reassigned to transfer the address for the second request. Assuming that this request is to a different memory module, we now have two modules proceeding with read access cycles in parallel. If neither module has finished with its access, the bus may be reassigned to a third request, and so on. Eventually, the first memory module completes its access cycle and uses the bus to transfer the word to the source that requested it. As other modules complete their cycles, the bus is used to transfer their data to the corresponding sources. Note that the actual length of time between address transfer and word return is not critical. Address and data transfers for different requests represent independent uses of the bus that can be interleaved in any order.

The split-transaction protocol allows the bus and the available bandwidth to be used more efficiently. The performance improvement achieved with this protocol depends on the relationship between the bus transfer time and the memory access time. Performance is improved at the cost of increased bus complexity. There are two reasons why complexity increases. Since a memory module needs to know which source initiated a given read request, a source identification tag must be attached to the request. This tag is later used to send the requested data to the source. Complexity also increases because all modules, not just the processors, must be able to act as bus masters.

Multiprocessors that use the split-transaction bus vary in size from 4 to 32 processors. In larger sizes, the bandwidth of the bus can become a problem. The bandwidth can be increased if a wider bus, that is, a bus that has more wires, is used. Most of the data transferred between processors and memory modules consist of cache blocks, where a block consists of a number of words. If the bus is wide enough to transfer several words at a time, then a complete block can be transferred more quickly than if the words are transferred one at a time. The Challenge multiprocessor from Silicon Graphics Corporation uses a bus that allows parallel transfer of 256 bits of data.

The main limitation of a single bus is that the number of modules that can be connected to the bus is not large. An ordinary bus functions well if no more than 10 to 15 modules are connected to it. Using a wider bus to increase the bandwidth allows the number of modules to be doubled. The bandwidth of a single bus is limited by contention for the use of the bus and by the increased propagation delays caused by electrical loading when many modules are connected. Networks that allow multiple independent transfer operations to proceed in parallel can provide significantly increased data transfer rates.

#### 12.4.2 Crossbar Networks

A versatile switching arrangement is shown in Figure 12.5. It is known as the *crossbar switch*, which was originally developed for use in telephone networks. For clarity of illustration, the switches in the figure are depicted as mechanical switches, although in practice these are electronic switches. Any module,  $Q_i$ , can be connected to any other module,  $Q_j$ , by closing an appropriate switch. Such networks, where there is a direct link between all pairs of nodes, are called *fully connected* networks. Many simultaneous transfers are possible. If n sources need to send data to n distinct destinations, then all

Figure 12.5 Crossbar interconnection network.

of these transfers can take place concurrently. Since no transfer is prevented by the lack of a communication path, the crossbar is called a *nonblocking switch*.

In Figure 12.5, we show just a single switch at each crosspoint. In an actual multiprocessor, however, the paths through the crossbar network are much wider. This means that many switches are needed at each crosspoint. Since the number of crosspoints is  $n^2$  in a network used to interconnect n modules, the total number of switches becomes large as n increases. This results in high cost and cumbersome implementation. Crossbars are attractive as interconnection networks when the number of interconnected nodes is not large.

One of the larger crossbar switches is found in Sun's E10000 system, in which 16 four-processor nodes are connected by a  $16 \times 16$  crossbar switch. It is also possible to use a multilevel crossbar switch, where a crossbar switch at level 1 connects to a crossbar switch at level 2, and so on. In this way it is possible to connect a larger number of processors. Such schemes are found in Fujitsu's VPP5000, Hitachi's SR8000, and NEC's SX-5 machines. A multilevel crossbar has become a popular choice for a high-performance interconnection medium.

#### **12.4.3** MULTISTAGE NETWORKS

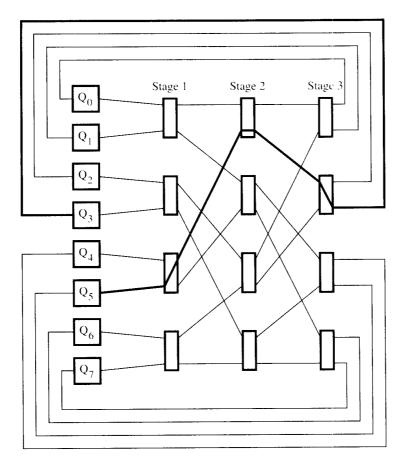

The bus and crossbar systems just described use a single stage of switching to provide a path from a source to a destination. It is also possible to implement interconnection networks that use multiple stages of switches to set up paths between sources and destinations. Such networks are less costly than the crossbar structure, yet they provide a reasonably large number of parallel paths between sources and destinations. Multistage switching is best illustrated by an example. Figure 12.6 shows a three-stage

Figure 12.6 Multistage shuffle network.

network called a *shuffle network* that interconnects eight modules. The term "shuffle" describes the pattern of connections from the outputs of one stage to the inputs of the next stage. This pattern is identical to the repositioning of playing cards in a deck that is shuffled by splitting the deck into two halves and interleaving the cards in each half.

Each switchbox in the figure is a  $2 \times 2$  switch that can route either input to either output. If the inputs request distinct outputs, then they can both be routed simultaneously in the straight-through or crossed pattern. If both inputs request the same output, only one request can be satisfied. The other one is blocked until the first request finishes using the switch. It can be shown that a network consisting of s stages can be used to interconnect  $2^s$  modules. In this case, there is exactly one path through the network from any module  $Q_i$  to any other module  $Q_j$ . Therefore, this network provides full connectivity between sources and destinations. Many request patterns, however, cannot be satisfied simultaneously. For example, the connection from  $Q_0$  to  $Q_4$  cannot be provided at the same time as the connection from  $Q_1$  to  $Q_5$ .

A multistage network is less expensive to implement than a crossbar network. If n nodes are to be interconnected using the scheme in Figure 12.6, then we must use  $s = \log_2 n$  stages with n/2 switchboxes per stage. Since each switchbox contains four switches, the total number of switches is

$$4 \times \frac{n}{2} \times \log_2 n = 2n \times \log_2 n$$

which, for large networks, is considerably less than the  $n^2$  switches needed in a crossbar network.

A particular request can be routed through the network using the following scheme. The source sends a binary pattern representing the destination number into the network. As the pattern moves through the network, each stage examines a different bit to determine switch settings. Stage 1 uses the most significant bit, stage 2 the middle bit, and stage 3 the least significant bit. When a request arrives on either input of a switch, it is routed to the upper output if the controlling bit is a 0 and to the lower output if the controlling bit is a 1. For example, a request from source  $Q_5$  for destination  $Q_3$  moves through the network as shown by the blue lines in Figure 12.6. Its route is controlled by the bit pattern 011, which is the destination address.

A good example of a multiprocessor based on a multistage network was the BBN Butterfly manufactured by BBN Advanced Computers. A 64-processor model of this system contained a three-stage network built with  $4\times 4$  switches. The routing through each stage of these switches was determined by successive 2-bit fields of the destination address. A current example is the IBM RS/6000 SP multiprocessor, which can use a multistage network as one of several options for interconnecting clusters of processors.

Multistage networks are less capable of providing concurrent connections than crossbar switches, but they are also less costly to implement. Interest in these networks peaked in the 1980s and has diminished greatly in the past few years. Other schemes, which we discuss in the remainder of this section, have become more attractive.

## 12.4.4 HYPERCUBE NETWORKS

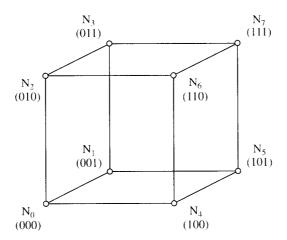

In the three schemes discussed previously, the interconnection network imposes the same delay for paths connecting any two modules. Such schemes can be used to implement UMA multiprocessors. We now discuss network topologies that are suitable only for NUMA multiprocessors. The first such scheme that gained popularity uses the topology of an *n*-dimensional cube, called a *hypercube*, to implement a network that interconnects 2<sup>n</sup> nodes. In addition to the communication circuits, each node usually includes a processor and a memory module as well as some I/O capability.

Figure 12.7 shows a three-dimensional hypercube. The small circles represent the communication circuits in the nodes. The functional units attached to each node are not shown in the figure. The edges of the cube represent bidirectional communication links between neighboring nodes. In an *n*-dimensional hypercube, each node is directly connected to *n* neighbors. A useful way to label the nodes is to assign binary addresses

**Figure 12.7** A 3-dimensional hypercube network.

to them in such a way that the addresses of any two neighbors differ in exactly one bit position, as shown in the figure.

Routing messages through the hypercube is particularly easy. If the processor at node  $N_i$  wishes to send a message to node  $N_j$ , it proceeds as follows. The binary addresses of the source, i, and the destination, j, are compared from least to most significant bits. Suppose that they differ first in position p. Node  $N_i$  then sends the message to its neighbor whose address, k, differs from i in bit position p. Node  $N_k$  forwards the message to the appropriate neighbor using the same address comparison scheme. The message gets closer to destination node  $N_j$  with each of these hops from one node to another. For example, a message from node  $N_2$  to node  $N_5$  requires 3 hops, passing through nodes  $N_3$  and  $N_1$ . The maximum distance that any message needs to travel in an n-dimensional hypercube is n hops.

Scanning address patterns from right to left is only one of the methods that can be used to determine message routing. Any other scheme that moves a message closer to its destination on each hop is equally acceptable, as long as the routing decision can be made at each node on the path using only local information. This feature of the hypercube is attractive from the reliability viewpoint. The existence of multiple paths between two nodes means that when faulty links are encountered, they can usually be avoided by simple, local routing decisions. If one of the shortest routes is not available, a message may be sent over a longer path. When this is done, care must be taken to avoid looping, which is the situation in which the message circulates in a closed loop and never reaches its destination.

Hypercube interconnection networks have been used in a number of machines. The better known examples include Intel's iPSC, which used a 7-dimensional cube to connect up to 128 nodes, and NCUBE's NCUBE/ten, which had up to 1024 nodes in a 10-dimensional cube. The hypercube networks lost much of their popularity in the early 1990s when mesh-based structures emerged as a more attractive alternative.

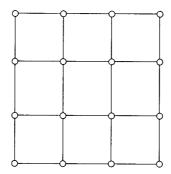

**Figure 12.8** A 2-dimensional mesh network.

## 12.4.5 MESH NETWORKS

One of the most natural ways of interconnecting a large number of nodes is by means of a *mesh*. An example of a mesh with 16 nodes is given in Figure 12.8. Again, the links between the nodes are bidirectional. Meshes gained popularity in the early 1990s and essentially displaced hypercubes as a choice for interconnection networks in large multiprocessors.

Routing in a mesh network can be done in several different ways. One of the simplest and most effective possibilities is to choose the path between a source node  $N_i$  and a destination node  $N_j$  such that the transfer first takes place in the horizontal direction from  $N_i$  toward  $N_j$ . When the column in which  $N_j$  resides is reached, the transfer proceeds in the vertical direction along this column. Well-known examples of mesh-based multiprocessors are Intel's Paragon and the experimental machines Dash [3] and Flash [4] at Stanford University and Alewife [5] at MIT.

If a wraparound connection is made between the nodes at the opposite edges in Figure 12.8, the result is a network that consists of a set of bidirectional rings in the *X* direction connected by a similar set of rings in the *Y* direction. In this network, called a *torus*, the average latency of information transfer is reduced, but at the cost of greater complexity. Such an interconnection network is used in Fujitsu's AP3000 machines.

Both the regular mesh and the torus schemes can also be implemented as three-dimensional networks, in which the links are between neighbors in the X, Y, and Z directions. An example of a three-dimensional torus is found in Cray's T3E multiprocessor.

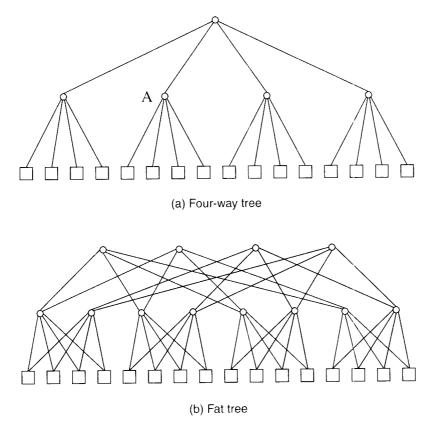

## 12.4.6 TREE NETWORKS

A hierarchically structured network implemented in the form of a tree is another interconnection topology. Figure 12.9*a* depicts a four-way tree that interconnects 16 modules. In this tree, each parent node allows communication between two of its children at a time. An intermediate-level node, for example node A in the figure, can provide a connection from one of its child nodes to its parent. This enables two leaf nodes that are

Figure 12.9 Tree-based networks.

any distance apart to communicate. Only one path at a time can be established through a given node in the tree.

A tree network performs well if there is a large amount of locality in communication, that is, if only a small portion of network traffic goes through the single root node. If this is not the case, performance deteriorates rapidly because the root node becomes a bottleneck.

To reduce the possibility of a bottleneck, the number of links in the upper levels of a tree hierarchy can be increased. This is done in a *fat tree* network, in which each node in the tree (except at the top level) has more than one parent. An example of a fat tree is given in Figure 12.9b. In this case, each node has two parent nodes. A fat tree structure was used in the CM-5 machine by Thinking Machines Corporation.

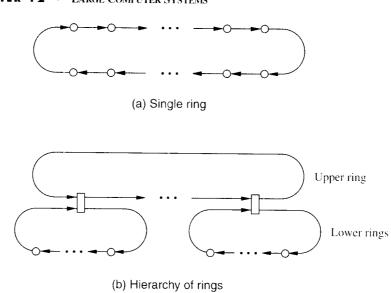

#### 12.4.7 RING NETWORKS

One of the simplest network topologies uses a ring to interconnect the nodes in the system, as shown in Figure 12.10a. The main advantage of this arrangement is that the ring is easy to implement. Links in the ring can be wide, usually accommodating

Figure 12.10 A ring-based interconnection network.

a complete packet in parallel, because each node is connected to only two neighbors. However, it is not useful to construct a very long ring to connect many nodes because the latency of information transfer would be unacceptably large.

Rings can be used as building blocks for the topologies discussed in previous sections, such as meshes, hypercubes, trees, and fat trees. We consider the simple possibility of using rings in a tree structure; this results in a hierarchy of rings as shown in Figure 12.10b. A two-level hierarchy is depicted in the figure, but more levels can be used. Having short rings reduces substantially the latency of transfers that involve nodes on the same ring. Moreover, the latency of transfers between two nodes on different rings is shorter than if a single ring were used. The drawback of this scheme is that the highest-level ring may become a bottleneck for traffic.

Commercial machines that feature ring networks include Exemplar V2600 by Hewlett-Packard and KSR-2 by Kendal Square Research. Rings have also been used in the experimental machines Hector [6] and NUMAchine [7] at the University of Toronto.

#### 12.4.8 PRACTICAL CONSIDERATIONS

We have seen that several different topologies can be used to implement the interconnection network in a multiprocessor system. It would be difficult to argue that any topology is clearly superior to others. Each has certain advantages and disadvantages. When comparing different approaches, we must take into account several practical considerations.

The most fundamental requirement is that the communication network be fast enough and have sufficient throughput to satisfy the traffic demand in a multiprocessor system. This implies high speed of transfer along the communication path and a simple routing mechanism to allow routing decisions to be made quickly. The network should be easy to implement; the wiring complexity must be reasonable and conducive to simple packaging. Complexity is inevitably reflected in the cost of the network, which is another major consideration.

Multiprocessors of different sizes are needed. The ideal network would be suitable for all sizes, ranging from just a few processors to possibly thousands of processors. The term *scalability* is often used to describe the ability of a multiprocessor architecture (which includes the interconnection network) to provide increased performance as the size of the system increases, while the increase in cost is proportional to the increase in size. It is particularly advantageous if a relatively small multiprocessor system can be acquired at a low cost but can be easily expanded to a large system with a linear increase in cost and performance. Unfortunately, this is not true for many commercial products. Often, the up-front cost for even a small system is large because much of the communication hardware needed to accommodate a larger system must be provided in one piece.

In addition to providing the basic communication between sources and destinations, it is useful to have *broadcasting* capability where a message traverses the entire network and is received by all nodes. The ability to send a message to only a subset of the network nodes is also beneficial. Such transfers are called *multicasting*.

The choice of the interconnection network affects the implementation of schemes used to ensure that any multiple copies of data that may exist in caches of different processors acquire the updates made so that all copies always have the same values. Such schemes are discussed in Section 12.6.2.

Reliability is another important factor. The more complex the network, the more likely it is to fail. Ideally, the machine could continue to function even if some link in the network fails. This is possible in networks that provide at least two different paths between each pair of communicating nodes. In general, simple networks tend to be robust, and they do not fail any more often than the processing and memory modules in the system. Highly reliable networks that include additional hardware can be built at considerable cost. This topic is beyond the scope of this book.

To demonstrate how all these characteristics can be evaluated, let us make a brief qualitative comparison of networks based on meshes and rings.

## Meshes and Rings

Both mesh and ring networks are characterized by point-to-point links (connecting adjacent nodes), which can be driven at high clock rates. Both are viable in small configurations and can be expanded without difficulty. Incremental expansion is simpler in a ring network than in a mesh network.

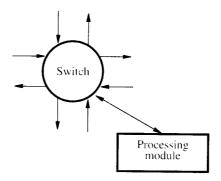

In Figures 12.8 and 12.10, we indicate the nodes in the network as small circles and the links as single lines. Consider a more detailed picture: Figure 12.11 shows the communication paths associated with one node that has a processing module attached to it. The switch block includes both the circuitry that selects the path for a transfer and the buffers needed to hold the data being transferred. Data are transferred from the buffer in one node to the buffer in the next node in one clock cycle. Figure 12.11a depicts a node in a two-dimensional mesh network. Since bidirectional communication is needed

(a) Node in a mesh

(b) Node in a ring

Figure 12.11 Nodes in mesh and ring networks.

in both the *X* and *Y* directions, eight distinct network links must be connected to the node. The width of these links is limited by the total number of wires that can be used, taking into account the cost and packaging. Thus, it is unlikely that an individual link could be wide enough to carry an entire packet in parallel. To deal with this constraint, a packet can be divided into smaller portions to correspond to the width of the link. The term *flit* (FLow control digIT) is often used to refer to a portion of the packet that can be accepted by the switching circuitry in the node for forwarding, or buffering in case the forward path is blocked by another transfer. In practice, it is convenient if the flit corresponds to the width of the link.

If a packet must be divided into flits, how should it be routed through the network? A straightforward scheme, known as the *store-and-forward* method, is to provide a large enough buffer in each node to hold all flits of a packet. Thus, an entire packet is transferred from one node to another, where it is stored until it can be forwarded to the next node. (The number of clock cycles required for the transfer depends on the number of flits.) The negative aspects of this scheme are the size of the buffers needed and the increased latency in passing through a node. An attractive alternative

is the *wormhole* routing scheme (which has also been referred to as *pipelining*), in which the sequence of flits that constitute a packet can be viewed as a *worm* that moves through the network. The first flit in a worm contains a *header* that includes the address of the destination node. As this flit moves through the network, it establishes a path along which the remaining flits will pass. The tail of the worm closes the established path. The head of the worm may be temporarily blocked at any node, because another worm may be passing through this node. However, once the head moves, the rest of the worm moves along in subsequent clock cycles. Some control mechanism must stop the transmission of flits from preceding nodes when the head of the worm is blocked; a simple scheme using two buffers per node for each direction of transfer has been developed for this purpose [8]. Wormhole routing has lower latency than storeand-forward routing because the head flit is sent on its way without waiting for the remaining flits of the packet.

Wormhole routing is an application of a strategy known as *circuit switching*, which is a familiar concept from telephone networks, where a path through the network is established when a number is dialed. The conversation takes place along this path, called a *circuit*. The circuit is deactivated when the calling party hangs up. In the case of wormhole routing, it is the head flit that establishes the path. The progression of this flit may be temporarily blocked as explained above. Once a circuit is established, however, the remaining flits of the packet move toward the destination without experiencing any contention. In contrast, strategies in which an entire packet is buffered at each node, as in the store-and-forward method, are called *packet switching*. In this case, no circuit is set up, and the packet moves through the network as the buffer in each node becomes available.

Connections to a node in a ring network are shown in Figure 12.11b. Here, transfer occurs in only one direction, in addition to the connection to the processing module. Thus, the width of the link can be four times that in a mesh network for the same wire count. This means that it is feasible for an entire packet to be transferred in parallel from one node to another in one clock cycle. Figure 12.11b shows a node in the lowest level ring, to which a processing module is attached. If a ring hierarchy such as that in Figure 12.10b is used, then the inter-ring interfaces between lower and upper rings will have two input and two output links, one of each belonging to the upper- and lower-level rings.

Routing in a hierarchical ring network is very simple. A packet is never blocked, except possibly at an inter-ring interface when incoming packets on both upper- and lower-level rings are destined to continue along just one of the rings. To handle this situation, buffers (queues) must be provided in the interface, one from the lower- to the upper-level ring and another in the opposite direction. A processing module may inject a new packet onto the ring whenever no packet is arriving to the node from its upstream neighbor.

Next we consider the ability of networks to broadcast or multicast data. This ability is naturally available in ring networks. For example, a packet can be broadcast to all nodes by sending it to the top-level ring. As the packet traverses this ring, a copy is made at each inter-ring interface and sent along to the next lower-level ring. This process is repeated at all levels so that the copies of the original packet visit all nodes in the lowest-level rings. Broadcasting in a mesh network is more difficult, because the broadcast packet has to be broken up into flits and the progress of the broadcast

worm may be blocked at various nodes by other traffic. Moreover, the completion of a broadcast is not easy to detect.

The main disadvantage of a hierarchical ring network is that the ring at the top of the hierarchy may become a bottleneck if too many packets need to be transferred over it. This will occur if the locality in communication is low. The limited bandwidth of the top-level ring restricts the scalability of systems based on such networks to hundreds of processors. In contrast, mesh-based systems scale well to thousands of processors.

The preceding discussion shows that both meshes and rings are good choices for interconnection networks. Ring-based systems are easier to implement, but do not scale as well as mesh-based systems. Thus, rings merit serious consideration if the maximum size of the system is a few hundred processors. Mesh systems are suitable for use in both small and very large systems. For very small systems, say, up to 16 processors, the most effective choices are a single bus or a crossbar switch.

Since the size of a multiprocessor system has important implications, the reader may wonder what range of systems are in practical use. Most multiprocessor systems are relatively small. Many machines are in the range of 4 to 128 processors. Some very large machines with thousands of processors exist. However, the market for such large machines is small.

## 12.4.9 MIXED TOPOLOGY NETWORKS

We have considered several possible network topologies and showed that all existing topologies have certain advantages and disadvantages. Designers of multiprocessor systems strive to achieve superior performance at a reasonable cost. In an effort to exploit the most advantageous characteristics of different topologies, many successful machines feature mixed topologies. Bus and crossbar are excellent choices for connecting a few processors together. So, we often see a cluster of processors, typically from 2 to 8, connected using a bus or a crossbar. Such clusters, usually referred to as nodes, are then interconnected using a suitable topology to form a larger system.

Data General's AV25000 system uses nodes where processors are connected by a bus. These nodes are then interconnected using a ring network. Hewlett-Packard's Exemplar V2600 also uses a ring network to interconnect nodes, where each node has a crossbar switch connecting the processors. Compaq's AlphaServer SC uses a fat tree to interconnect the nodes that comprise processors connected by a crossbar switch.

## 12.4.10 SYMMETRIC MULTIPROCESSORS

Consider a multiprocessor system in which all processors have identical access to all memory modules and all I/O devices, so that the operating system software can treat any processor as interchangeable with any other processor. Then, if any processor can execute either the operating system kernel or user programs, the machine is called a *symmetric multiprocessor* (SMP). This also implies that any processor can initiate an I/O operation on any I/O device, and it can handle any external interrupt.

SMPs are usually implemented using either a bus or a crossbar network. Often, an SMP is used as a node in a much larger multiprocessor system. For example, SMP nodes are used in the Exemplar V2600 and AlphaServer SC multiprocessors mentioned above.

## 12.5 MEMORY ORGANIZATION IN MULTIPROCESSORS

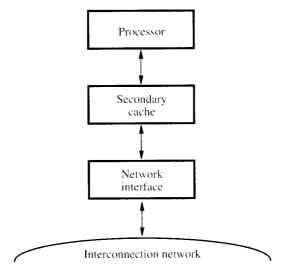

In Chapter 5 we saw that the organization of the memory in a uniprocessor system has a large impact on performance. The same is true in multiprocessor systems. To exploit the locality of reference phenomenon, each processor usually includes a primary cache and a secondary cache. If the organization in Figure 12.2 is used, then each processor module can be connected to the communication network as shown in Figure 12.12. Only the secondary cache is shown in the figure since the primary cache is assumed to be a part of the processor chip. The memory modules are accessed using a single *global address space*, where a range of physical addresses is assigned to each memory module. In such a *shared memory* system, the processors access all memory modules in the same way. From the software standpoint, this is the simplest use of the address space.

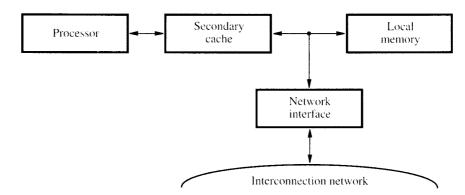

In NUMA-organized multiprocessors, shown in Figure 12.3, each node contains a processor and a portion of the memory. A natural way of implementing the node is illustrated in Figure 12.13. In this case, it is also convenient to use a single global address space. Again, the processor accesses all memory modules in the same way, but

Figure 12.12 A processor node for the multiprocessor organization in Figure 12.2.

Figure 12.13 Node structure for the multiprocessor organization in Figure 12.3.

the accesses to the local memory component of the global address space take less time to complete than accesses to remote memory modules.

In the organization of Figure 12.4, each processor accesses directly only its own local memory. Thus, each memory module constitutes the *private address space* of one processor; there is no global address space. Any interaction among programs or processes running on different processors is implemented by sending *messages* from one processor to another. In this form of communication, each processor views the interconnection network as an I/O device. In effect, each node in such a system behaves as a computer in the same manner as discussed in previous chapters for uniprocessor machines. For this reason, systems of this type are referred to also as *multicomputers*. This organization provides the easiest way to connect a number of computers into a large system. Communication between tasks running on different computers is relatively slow because the exchange of messages requires software intervention. We consider this type of system in Section 12.7.

When data are shared among many processors, we must ensure that the processors observe the same value for a given data item. The presence of many caches in a shared-memory system creates a problem in this respect. Multiple copies of some data items may exist in various caches. Whenever a processor changes (writes) a data item in its own cache, the same change must be made in all caches that have a copy. Alternatively, the other copies must be invalidated. In other words, shared data must be *coherent* in all caches in the system. The problem of maintaining cache coherence can be solved in several different ways. We examine the most popular solutions in Section 12.6.2.

## 12.6 PROGRAM PARALLELISM AND SHARED VARIABLES

The introduction to this chapter states that it is difficult to break large tasks down into subtasks that can be executed in parallel on a multiprocessor. In some special cases, however, this division is easy. If a large task originates as a set of independent programs, then these programs can simply be executed on different processors. Unless

Figure 12.14 Parallel programming construct.

these programs block each other in competing for shared I/O devices, the multiprocessor is fully used by such a workload.

Another easy case occurs when a high-level source programming language has constructs that allow an application programmer to explicitly declare that certain subtasks of a program can be executed in parallel. Figure 12.14 shows such a construct, often called a PAR segment. The PARBEGIN and PAREND control statements bracket a list of procedures, named Proc1 through Proc*K*, that can be executed in parallel. The order of execution of this program is as follows. When the segment of the program preceding the PARBEGIN statement is completed, any or all of the *K* parallel procedures can be started immediately, depending on the number of idle processors available. They can be started in any order. Execution of the part of the program following PAREND is allowed to begin only after all of the *K* procedures have completed execution.

If this program is the only one being executed on the multiprocessor, then the burden of using the processors efficiently is placed on the application programmer. The degree of parallelism, K, of the PAR segments and their total size relative to the sequential segments determine the level of utilization achievable by the multiprocessor.

The most challenging task in achieving high utilization of multiprocessor systems is to develop compilers that can automatically detect parallelism in a user program. The usefulness of automatic detection of parallelism is based on the following reasoning. An application programmer naturally visualizes a program as a set of serially performed operations. However, even though the programmer specifies the operations as a serial list of instructions in some high-level language, many opportunities may exist for executing various groups of instructions in parallel. A simple example is that of successive passes through a loop. If no data dependency is involved between different iterations of the loop, then successive passes can be executed in parallel. On the other hand, if the first pass through the loop generates data that are needed in the second pass, and so

on, then parallel execution is not possible. Data dependencies must be detected by the compiler to determine which operations can be performed in parallel and which cannot. The design of compilers that can detect parallelism is complex. Even after the parallel parts of a program are identified, their subsequent scheduling for execution on a multiprocessor with a limited number of processors is a nontrivial task. Scheduling may be done either by the compiler or at runtime by the operating system. We do not pursue this topic of determining and scheduling tasks that can be executed in parallel. Instead, we turn to the issue of accessing shared variables that are modified by programs running in parallel on different processors of a multiprocessor system.

## 12.6.1 ACCESSING SHARED VARIABLES

Assume that we have identified two tasks that can run in parallel on a multiprocessor. The tasks are largely independent, but from time to time they access and modify some common, shared variable in the global memory. For example, let a shared variable SUM represent the balance in an account. Moreover, assume that several tasks running on different processors need to update this account. Each task manipulates SUM in the following way: The task reads the current value from SUM, performs an operation that depends on this value, and writes the result back into SUM. It is easy to see how errors can occur if such *read-modify-write* accesses to SUM are performed by tasks T1 and T2 running in parallel on processors P1 and P2. Suppose that both T1 and T2 read the current value from SUM, say 17, and then proceed to modify it locally. T1 adds 5 for a result of 22, and T2 subtracts 7 for a result of 10. They then proceed to write their individual results back into SUM, with T2 writing first followed by T1. The variable SUM now has the value 22, which is wrong. SUM should contain the value 15 (= 17 + 5 - 7), which is the intended result after applying the modifications strictly one after the other, in either order.

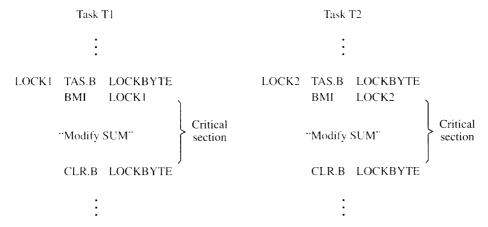

To guarantee correct manipulation of the shared variable SUM, each task must have exclusive access to it during the complete read-modify-write sequence. This can be provided by using a global lock variable, LOCK, and a machine instruction called Test-and-Set. The variable LOCK has two possible values, 0 or 1. It serves as a guard to ensure that only one task at a time is allowed access to SUM during the time needed to execute the instructions that update the value of this shared variable. Such a sequence of instructions is called a *critical section*. LOCK is manipulated as follows. It is equal to 0 when neither task is in its critical section that operates on SUM. When either task wishes to modify SUM, it first checks the value of LOCK and then sets it to 1, regardless of its original value. If the original value was 0, then the task can safely proceed to work on SUM because no other task is currently doing so. On the other hand, if the original value of LOCK was 1, then the task knows that some other task is operating on SUM. It must wait until that task resets LOCK to 0 before it can proceed. This desired mode of operation on LOCK is made foolproof by the Test-and-Set instruction. As its name implies, this instruction performs the critical steps of testing and setting LOCK in an indivisible sequence of operations executed as a single machine instruction. While this instruction is executing, the memory module involved must not respond to access requests from any other processor.

Figure 12.15 Mutually exclusive access to critical sections.

As a specific example, consider the Test-and-Set instruction denoted as TAS in the Motorola 68000 microprocessor. This instruction has one operand that is always a byte. Assume that it is stored in the memory at location LOCKBYTE. Bit  $b_7$ , the most significant bit of this operand, serves as the variable LOCK just discussed. The TAS instruction performs the uninterruptible test and set operations on bit  $b_7$ . Condition code flag N (Negative) is set to the original value of  $b_7$ . Thus, after the execution of TAS is completed, the program can continue into its critical section if N equals 0. but it must wait if N equals 1. Figure 12.15 shows how two tasks, T1 and T2, can manipulate LOCKBYTE to enter critical sections of code in which they update the shared variable SUM. The TAS instruction is followed by a conditional branch instruction. This instruction causes a branch back to TAS if N = 1, resulting in a wait loop that continues to execute TAS on the operand in location LOCKBYTE until it finds  $b_7$  equal to 0. The branch instruction fails if TAS is executed when  $b_7$  is 0, allowing the program to continue into its critical section. When execution of the critical section is completed, LOCKBYTE is cleared. As a result, bit  $b_7$  is reset to 0, allowing any waiting program to proceed into its critical section.

The TAS instruction is an example of a simple machine instruction that can be used to implement a lock. Most computers include an instruction of this type. These instructions may provide additional capabilities, such as incorporating a conditional branch based on the result of the test.

## 12.6.2 CACHE COHERENCE

Shared data leads to another problem in a multiprocessor machine; the presence of multiple caches means that copies of shared data may reside in several caches. When any processor writes to a shared variable in its own cache, all other caches that contain a copy of that variable will then have the old, incorrect value. They must be informed of the change so that they can either update their copy to the new value or invalidate it.

Cache coherence is defined as the situation in which all cached copies of shared data have the same value at all times.

In Chapter 5 we discussed two basic approaches for performing write operations on data in a cache. The write-through approach changes the data in both the cache and the main memory. The write-back approach changes the data only in the cache; the main memory copy is updated when a dirty data block in the cache has to be replaced. Similar approaches can also be used in a multiprocessor system.

#### **Write-Through Protocol**

A write-through protocol can be implemented in two fundamental versions. One version is based on updating the values in other caches, while the second relies on invalidating the copies in other caches.

Let us consider the *write-through with update* protocol first. When a processor writes a new value into its cache, the new value is also written into the memory module that holds the cache block being changed. Since copies of this block may exist in other caches, these copies must be updated to reflect the change caused by the write operation. Conceptually, the simplest way of doing this is to broadcast the written data to all processor modules in the system. As each processor module receives the broadcast data, it updates the contents of the affected cache block if this block is present in its cache (primary or secondary).

The second version of write-through protocol is based on *invalidation* of copies. When a processor writes a new value into its cache, this value is written into the memory module, and all copies in other caches are invalidated. Again, broadcasting can be used to send the invalidation requests throughout the system.

#### **Write-Back Protocol**

In the write-back protocol, multiple copies of a cache block may exist if different processors have loaded (read) the block into their caches. If some processor wants to change this block, it must first become an exclusive owner of this block. When the ownership is granted to this processor by the memory module that is the home location of the block, all other copies, including the one in the memory module, are invalidated. Now the owner of the block may change the contents at will without having to take any other action. When another processor wishes to read this block, the data are sent to this processor by the current owner. The data are also sent to the home memory module, which reacquires ownership and updates the block to contain the latest value.

The write-back protocol causes less traffic than the write-through protocol, because a processor is likely to perform several writes to a cache block before this block is needed by another processor.

So far, we have assumed that update and invalidate requests in these protocols are broadcast through the interconnection network. Whether it is practical to implement such broadcasts depends largely on the structure of the interconnection network. The most natural network for supporting broadcasting is the single bus, discussed in Section 12.4.1. In small multiprocessors that use a single bus, cache coherence can be realized using a scheme known as snooping.

#### **Snoopy Caches**

In a single-bus system, all transactions between processors and memory modules occur via the bus. In effect, they are broadcast to all units connected to the bus. Suppose that each cache associated with a processor has a controller circuit that observes the transactions on the bus that involve other processors. Suppose also that the write-back protocol just described is used.

Whenever a processor writes to its cache block for the first time, the cache block is marked as dirty, and the write is broadcast on the bus. The memory module and all other caches invalidate their copies. The processor that performed the write is now the owner of the cache block. It can do further writes in the same block without broadcasting them. If another processor issues a read request for the same block, the memory module cannot respond because it does not have a valid copy. But the present owner also sees this request when it appears on the bus, and it must supply the correct value to the requesting processor. The memory module is informed that an owner is supplying the correct value by a broadcast signal from the owner (which includes the data that the owner places on the bus), and the memory updates its value. Finally, the owner marks its copy as clean. Operation now proceeds with multiple caches and the memory module all having the correct value of the block. In the case in which a dirty value must be replaced to make room in the cache for a new block, a write-back operation to the memory module must be performed.

If two processors want to write to the same cache block at the same time, one of the processors will be granted the use of the bus first and will become the owner. As a result, the other processor's copy of the cache block will be invalidated. The second processor can then repeat its write request. This sequential handling of write requests ensures that the two processors can correctly change different words in a given cache block.

The scheme just described is based on the ability of cache controllers to observe the activity on the bus and take appropriate actions. We refer to such schemes as *snoopy-cache* techniques.

For performance reasons, it is important that the snooping function not interfere with the normal operation of a processor and its cache. Such interference would occur if, for each request on the bus, the cache controller had to access the tags of its cache to see if the block in question is present in the cache. In most cases, the answer would be negative. To eliminate unnecessary interference, each cache can be provided with a set of duplicate tags, which maintain the same status information about the blocks in the cache but can be accessed separately by the snooping circuitry.

While the concept of snoopy caches is effective and simple to implement, it is suitable only for single-bus systems. In larger multiprocessors, more complex arrangements must be used.

#### **Directory-Based Schemes**

Enforcing cache coherence using a broadcast mechanism for distribution of invalidation or update requests becomes less attractive as the multiprocessor system grows in size. The main reason is that a large amount of unnecessary traffic may be generated by a full broadcast because, in practical applications, copies of a given block are usually present in only a few caches.

A useful alternative is to keep a *directory* of the locations, that is, the caches where copies exist at any given time. One way to implement a directory scheme is to include additional status bits for each block in a particular memory module, which indicate the caches where copies of this block may be found. Then, instead of broadcasting to all caches, the memory module can send individual messages, or a multicast such as an invalidate request in the write-back protocol, to only those caches that have a copy. Of course, the additional bits in the memory modules increase the cost of these modules. Different versions of directory schemes have been proposed and some have been implemented in existing multiprocessor systems.

#### SCI Standard

A specific approach to cache coherence has been standardized by the Institute of Electrical and Electronics Engineers (IEEE). It is a part of the SCI (Scalable Coherent Interface) standard [9], which defines a multiprocessor backplane that is intended to provide fast signaling, scalable architecture, cache coherence, and simple implementation. The interconnection network uses point-to-point links, and the communication protocol is based on a single-requester single-responder principle. A packet originates at a source node and is addressed to a single target. If a packet sent by the source is accepted by the target, the latter returns a positive acknowledgement packet. If the packet is not accepted, then a negative acknowledgement is returned, which causes a retry.

Cache coherence is achieved using a distributed directory-based protocol. A doubly-linked list is established for each cache block that contains shared data. Each processor node that caches a given block of shared data includes pointers to the previous and to the next nodes that share the block. These pointers are part of the cache-block tag. The head of this doubly-linked list has a pointer to the memory module that holds the block. When a new node accesses the memory module to read this block, the node becomes the new head of the list and the memory directory is updated by replacing the pointer to the previous head with the address of the new head. A write access to the memory can be performed only by the head of the list. If another node wishes to perform a write, it can do so by inserting itself at the head of the list and purging the rest of the entries in the list.

The SCI cache coherence scheme scales well because the memory directory and the processor cache-tag storage requirements do not increase as the size of the linked list increases. The disadvantage of this scheme is that this additional storage presents a costly fixed overhead that is incurred in all cases.

Although the SCI standard does not specify a particular topology for the interconnection network, the ring topology is one of the natural choices. Hewlett-Packard's Exemplar V2600 and Data General's AV25000 multiprocessors use a ring topology and implement the coherence protocol described above.

## **CC-NUMA Multiprocessors**

Cache coherence is an important issue in multiprocessor systems. It has been the topic of extensive research. We have briefly described some key implementation schemes. Many subtle details are beyond the scope of this book.

A multiprocessor may have the cache coherence implemented either in hardware or in software. From the performance point of view, it is advantageous to have hardware-controlled cache coherence. Most of the current NUMA multiprocessors have cache coherence implemented in hardware. They are often referred to as *cache-coherent NUMA* (CC-NUMA) systems.

### 12.6.3 NEED FOR LOCKING AND CACHE COHERENCE

We should note that the requirement for lock guard controls on access to shared variables is independent of the need for cache coherence controls — both types of controls are needed. Consider a situation in which cache coherence is maintained by using the write-through policy accompanied by cache updating of writes to shared variables. Suppose that the contents of SUM in the example in Section 12.6.1 have been read into the caches of the two processors that execute tasks T1 and T2. If the read operations are part of an update sequence and are not made mutually exclusive by the use of a lock guard control, then the original error can still occur. If task T1 writes its new value last, as before, then SUM will contain the value 22, which is wrong. Cache coherence is maintained throughout this sequence of events. However, incorrect results are obtained because lock guard controls are not used.

## 12.7 MULTICOMPUTERS

In Section 12.5 we introduced the concept of multicomputers. We now examine the salient features of such systems in more detail.

A multicomputer system is structured as shown in Figure 12.4. Each processing node in the system is a self-contained computer that communicates with other processing nodes by sending messages over the network. Systems of this type are often called *message-passing systems*, in contrast to the shared-memory multiprocessors discussed previously.

In multicomputer systems, the demands on the interconnection network are less stringent than in shared-memory multiprocessor systems. A shared-memory machine must have a fast network with high bandwidth because processor modules frequently access the remote memory modules that constitute the shared memory. A slow network would quickly become a bottleneck, and performance would severely degrade.

In a multicomputer, messages are sent much less frequently, resulting in much less traffic than in the shared-memory systems. Therefore, a simpler and less expensive network can be used. In view of this disparity in the intensity of communication, the terms *tightly coupled* and *loosely coupled* have also been associated with shared-memory and message-passing systems, respectively.

Any network described in Section 12.4 can be used in a multicomputer system. Since the traffic demands are relatively modest, the physical implementation of the interconnection network is likely to be inexpensive. The links in the network often involve bit-serial lines driven by I/O device interfaces. An interface circuit reads a

message from the memory of the source computer using the DMA technique, converts it into a bit-serial format, and transmits it over the network to the destination computer. Source and destination addresses are included in a header of the message for routing purposes. The message is routed to the destination computer where it is written into a memory buffer by the I/O interface of that computer.

In the 1980s, hypercube-based interconnection networks were very popular. Such networks were used in several message-passing multiprocessor systems, typically using bit-serial transmission. Examples of such machines are Intel's iPSC, NCUBE's NCUBE/ten, and Thinking Machines' CM-2. Then in the early 1990s, other topologies gained popularity for both message-passing and shared-memory machines. Thinking Machines' CM-5 is an example of a message-passing machine that uses a fat tree network with a link width of four. Intel's Paragon uses a mesh network with a link width of 16. To facilitate message passing, it is useful to include a special communications unit at each node in the network. For example, the Paragon machine has a message processor that essentially frees the application processor from having to be involved in the details of message handling.

## 12.7.1 LOCAL AREA NETWORKS

Because the communication demands in a multicomputer system are relatively low. we can consider replacing the specialized interconnection network with some readily available standard network that was developed for more general communication purposes. Many networks exist for interconnecting various types of computing equipment. Networks that span a small geographic area with distances not exceeding a few kilometers are called *local area networks* (LANs). Networks that cover larger areas that involve distances up to thousands of kilometers are referred to as *long-haul networks*, or *wide area networks*.

The most popular LANs use either the bus or the ring topology. The transmission media for either bus or ring LANs can be twisted wire pair, coaxial cable, or optical fiber. Bit-serial transmission is used, and rates range from ten to hundreds of megabits per second. Only one message packet at a time can be successfully transmitted on the single shared path. Source and destination device addresses precede the data field of a packet, and appropriate delimiters indicate the start and end of the packet. In general, packets have variable lengths ranging from tens of bytes to over 1000 bytes.

A protocol that implements distributed access control is needed to ensure orderly transfer of packets between arbitrary pairs of communicating devices. We will sketch the basic ideas involved in two widely used protocols — the Ethernet bus and the token ring. These protocols are specified in detail in IEEE standards [10].

## 12.7.2 ETHERNET (CSMA/CD) BUS

The Ethernet bus access protocol, also called the Carrier Sense Multiple Access with Collision Detection (CSMA/CD) protocol, is conceptually one of the simplest protocols. Whenever an attached device has a message to transmit, it waits until it senses that the

bus is idle and then begins transmission. The device then monitors the bus for  $2\tau$  seconds as it transmits its message, where  $\tau$  is the end-to-end bus propagation delay. If the device does not observe any distortion of its transmitted signal during the  $2\tau$  interval, then it assumes that no other station has started transmission and continues its transmission to completion. On the other hand, if distortion is observed, caused by the beginning of a transmission from some other device, then both devices must stop transmitting. The mutually destructive distortion of the two transmitted signals is called a *collision*, and the time interval  $2\tau$  is called the *collision window*.

Messages that have been destroyed by collision must be retransmitted. If the devices involved in the collision attempt to retry immediately, their packets will almost certainly collide again. A basic strategy used to prevent collision of the retries is as follows. Each device independently waits for a random amount of time, then waits until the bus is idle and begins retransmission. If the random waits are a few multiples of  $2\tau$ , the probability of repeated collisions is reduced.

## **12.7.3 TOKEN RING**

The token-ring protocol is used for ring networks. A single, appropriately encoded short message, called a *token*, circulates continuously around the ring. The arrival of the token at a ring node represents permission to transmit. If the node has nothing to transmit, it forwards the token to the next node downstream with as little delay as possible. If the node has data ready for transmission, it inhibits propagation of the token. Instead it transmits a packet of information preceded by an appropriately encoded header flag. As the packet is transmitted around the ring, its contents are read and copied as it travels past the destination node. The packet continues to travel around the ring until it reaches the source node, where it is discarded. When the source node completes transmitting a packet, it releases the token, which again starts to circulate around the ring. The packet size on a token ring is variable and is limited only by the amount of buffer memory available in each node because the destination node must be able to store complete packets.

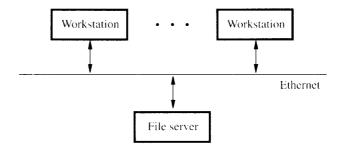

The main reason for considering the standard LANs in the context of multicomputer systems is not because they can be used in self-contained systems that we have been discussing, but because they can be used in conjunction with standard workstations to conveniently form a multicomputer system.

#### 12.7.4 NETWORK OF WORKSTATIONS

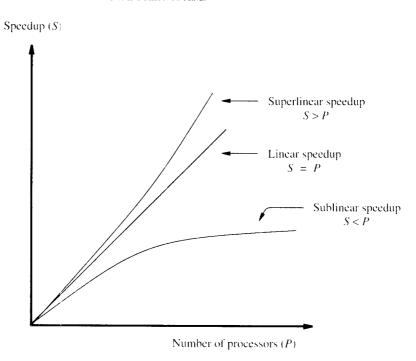

Today, most commercial, educational, and government organizations have a collection of workstations to meet their computing needs. These workstations are usually connected to a LAN that allows access to fileservers, printers, and specialized computing resources. (See Figure 12.16.)